Understanding the Cell Microprocessor

by Anand Lal Shimpi on March 17, 2005 12:05 AM EST- Posted in

- CPUs

Understanding Gates

The fundamental building blocks of any microprocessor are gates. Gates are collections of transistors that electrically mimic a particular logic function. For example, a 2-input AND gate will take two input signals and output a 1 only if the two inputs are both 1s. An XOR gate will output a 1 only if the two inputs are different. A NOR gate will output a 1 only if all inputs are 0s.Combinations of these gates are used to implement everything in a microprocessor, including functional units like adders, multipliers, etc.

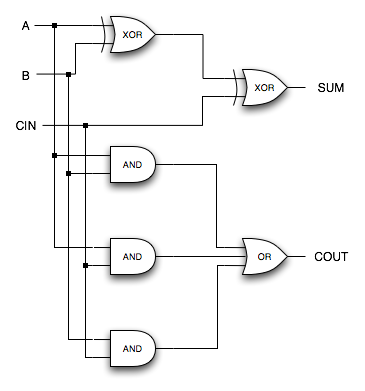

Here, we have a 1-bit carry adder implemented using logic gates. It will add any two 1-bit numbers and produce a result.

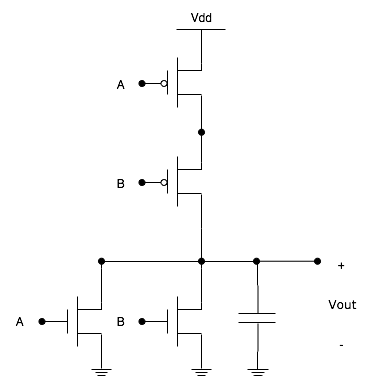

A very popular way of designing gate logic is using what is known as static CMOS. Static CMOS designs are relatively easy to implement and there are tons of libraries available for automated (e.g. computer driven) static CMOS design. There are a couple of problems with static CMOS design:

- Static CMOS circuits aren’t the fastest circuits possible, which is why they aren’t used in things like Intel’s double-pumped ALUs where high clock speeds are necessary.

- Static CMOS designs use quite a few transistors. For each m-input gate, you need 2 * m transistors (m PMOS and m NMOS transistors), which for high fan-in gates (gates with lots of inputs), it drives transistor counts up considerably. As is the case with any heavily SIMD architecture, high fan-in gates are commonplace.

There’s another problem here - the NOR gate isn’t clocked. Normally, large collections of gates are assembled and put behind an element called a latch, which is clocked. One type of large collection would be all of the circuitry used for a pipeline stage. This isn’t really a problem for static CMOS gates, as it greatly simplifies the distribution of clocks to the chip (since you don’t have to route a clock signal to every gate, just every latch, and there are far more general gates than there are latches).

Designing and implementing static CMOS gates are extremely easy. Hardware Description Languages (HDLs), programming languages in which chips are “written” have widespread static CMOS libraries, meaning that a chip designer can focus on writing code to crank out a chip without having to hand design its circuits. But as success is usually proportional to difficulty, static CMOS designs aren’t the fastest things in the world. Things like Intel’s 7.2GHz ALUs aren’t designed using static CMOS logic, neither is Cell.

70 Comments

View All Comments

faboloso112 - Thursday, March 17, 2005 - link

ahh i love bedtime stories!great read...VERY informative!

ksherman - Thursday, March 17, 2005 - link

sweet article! way over my head, but there were some parts that were dropped down to my level of understanding. Leave it to anand to tell the real story. It will be interesting to see how willing some companies will be to accomidate Sony's ratical processor... bu tas long as theirs money... Do you think that it is possible to (down the road) flop a x86 chip in place of the PPE? wouldn't hat make the Cell compatible with the current processing standards?ProviaFan - Thursday, March 17, 2005 - link

Describing this as a "sit down read" type of article makes me want to print it out to put it in the magazine rack, because I don't have a laptop + 802.11g to peruse AnandTech while I'm, er... ;)xsilver - Thursday, March 17, 2005 - link

nice, definitley one of those "sit down reads".... some serious shiznit ;)cosmotic - Thursday, March 17, 2005 - link

OMG! FIRST POST LOL ROFL LMAO OMG!!! LOOK WHOS COOL!!!Fricardo - Thursday, March 17, 2005 - link

Finally! Thanks guys.Bawl - Saturday, January 25, 2014 - link

I just love this deep analysis of one of the most mist-understanding processor of the last decade.Too bad that after spending more than a half-of-billion dollars, SonyThoshibaIBM didn't release the presumably outstanding CellTwo.

Ferrx - Sunday, December 20, 2015 - link

Hi, can you help me to understand this ? I don't understand at all about these._______ _________ ______

|Decode| | Execute | | Write |

----------- ---------------- -----------

| I1 | I2 | | | | | | | |

| I3 | I4 | | I1 | I2 | | | | |

| I3 | I4 | | I1 | | | | I2 | |

| | I4 | | | | | | I1 | I3 |

| I5 | I6 | | | | I4 | | I4 | |

| | I6 | | | I5 | | | I5 | |

| | | | | I6 | | | I6 | |

_______ _________ ______

In "Decode", each row has 2 columns. What do First and Second Column mean ?

same as "Write"

And in "Execute, each row has 3 columns. What do First, Second and Third column mean ?

And how is the process ? (The current table is about "In-Order Issue with Out-of-Order Completion").

I've read it many times, in the "Instruction Level Parallelism". But I still don't have any idea about it.

Ferrx - Sunday, December 20, 2015 - link

Hi, can you help me to understand this ? I don't understand at all about these._______ _________ ______

|Decode| | Execute | | Write |

----------- ---------------- -----------

| I1 | I2 | | | | | | | |

| I3 | I4 | | I1 | I2 | | | | |

| I3 | I4 | | I1 | | | | I2 | |

| | I4 | | | | | | I1 | I3 |

| I5 | I6 | | | | I4 | | I4 | |

| | I6 | | | I5 | | | I5 | |

| | | | | I6 | | | I6 | |

_______ _________ ______

In "Decode", each row has 2 columns. What do First and Second Column mean ?

same as "Write"

And in "Execute, each row has 3 columns. What do First, Second and Third column mean ?

And how is the process ? (The current table is about "In-Order Issue with Out-of-Order Completion").

I've read it many times, in the "Instruction Level Parallelism". But I still don't have any idea about it.

Ferrx - Sunday, December 20, 2015 - link

Aww... Can't do tab-'ing' 0__0