Opening the Kimono: Intel Details Nehalem and Tempts with Larrabee

by Anand Lal Shimpi on March 17, 2008 5:00 PM EST- Posted in

- CPUs

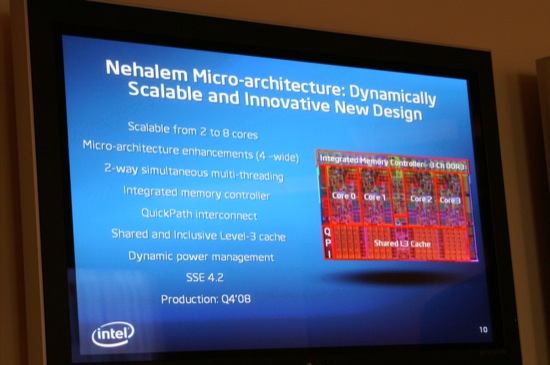

Nehalem supports QPI and features an integrated memory controller, as well as a large, shared, inclusive L3 cache.

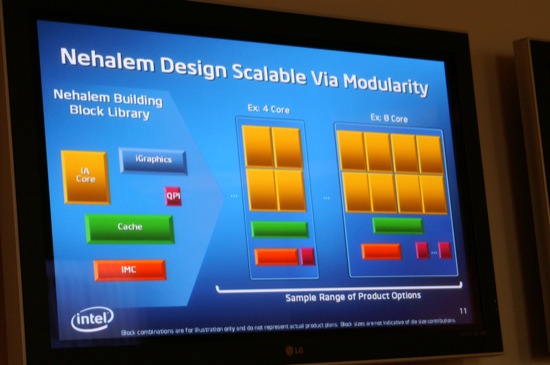

Nehalem is a modular architecture, allowing Intel to ship configurations with 2 - 8 cores, some may have integrated graphics and with various memory controller configurations.

Nehalem allows for 33% more micro-ops in flight compared to Penryn (128 micro-ops vs. 96 in Penryn), this increase was achieved by simply increasing the size of the re-order window and other such buffers throughout the pipeline.

With more micro-ops in flight, Nehalem can extract greater instruction level parallelism (ILP) as well as support an increase in micro-ops thanks to each core now handling micro-ops from two threads at once.

Despite the increase in ability to support more micro-ops in flight, there have been no significant changes to the decoder or front end of Nehalem. Nehalem is still fundamentally the same 4-issue design we saw introduced with the first Core 2 microprocessors. The next time we'll see a re-evaluation of this front end will most likely be 2 years from now with the 32nm "tock" processor, codenamed Sandy Bridge.

Nehalem also improved unaligned cache access performance. In SSE there are two types of instructions: one if your data is aligned to a 16-byte cache boundary, and one if your data is unaligned. In current Core 2 based processors, the aligned instructions could execute faster than the unaligned instructions. Every now and then a compiler would produce code that used an unaligned instruction on data that was aligned with a cache boundary, resulting in a performance penalty. Nehalem fixes this case (through some circuit tricks) where unaligned instructions running on aligned data are now fast.

In many applications (e.g. video encoding) you're walking through bytes of data through a stream. If you happen to cross a cache line boundary (64-byte lines) and an instruction needs data from both sides of that boundary you encounter a latency penalty for the unaligned cache access. Nehalem significantly reduces this latency penalty, so algorithms for things like motion estimation will be sped up significantly (hence the improvement in video encode performance).

Nehalem also introduces a second level branch predictor per core. This new branch predictor augments the normal one that sits in the processor pipeline and aids it much like a L2 cache works with a L1 cache. The second level predictor has a much larger set of history data it can use to predict branches, but since its branch history table is much larger, this predictor is much slower. The first level predictor works as it always has, predicting branches as best as it can, but simultaneously the new second level predictor will also be evaluating branches. There may be cases where the first level predictor makes a prediction based on the type of branch but doesn't really have the historical data to make a highly accurate prediction, but the second level predictor can. Since it (the 2nd level predictor) has a larger history window to predict from, it has higher accuracy and can, on the fly, help catch mispredicts and correct them before a significant penalty is incurred.

The renamed return stack buffer is also a very important enhancement to Nehalem. Mispredicts in the pipeline can result in incorrect data being populated into Penryn's return stack (a data structure that keeps track of where in memory the CPU should begin executing after working on a function). A return stack with renaming support prevents corruption in the stack, so as long as the calls/returns are properly paired you'll always get the right data out of Nehalem's stack even in the event of a mispredict.

53 Comments

View All Comments

haplo602 - Tuesday, March 18, 2008 - link

I wonder what the real world usage will be. I mean first you need to get Microsoft to code a new version of Windows to eat all that horse power. Then you are back at the begining... You have more cores but Windows is using most of them again (or not using all of them in case of old version).Anyway I don't see any significant benefits of these CPUs except highend server and workstation load.

Consumer will drift more into the console or memory/specialised processing unit (GPU, sound processors ...) markets ...

oldhoss - Tuesday, March 18, 2008 - link

The screwdriver is actually fuel for the IFRPS (Intel Fusion Reactor power supply), rated @ 1.21 Jigawatts! ;-Pbrshoemak - Monday, March 17, 2008 - link

I assume I'm not the only one who notices the glass of OJ on the 4 core Nehalem system? Kinda odd as I doubt they carry a lot of spares around.ryback - Tuesday, March 18, 2008 - link

It's not OJ. It's a screwdriver.tmouse - Tuesday, March 18, 2008 - link

Its part of the new processor cooling system. Also Intel's additional strategy Tick, Tock, Crock : enough alcohol = even BETTER coverage by the press ;)7Enigma - Tuesday, March 18, 2008 - link

HAHAHAHA! Very nice.Imaginer - Monday, March 17, 2008 - link

With intel doing things that way, I would expect the PC platform to finally have a standard instruction set for graphics processing similar to general purpose computing with the x86 standard. Would that mean that it would be ALOT EAISER for game developers to produce for the PC akin the way they are doing right now specializing for a particular console?I like that idea very much. Hopefully AMD/ATi and Nvidia would eventually be in on the standard as well.

Griswold - Tuesday, March 18, 2008 - link

I too think you got it all wrong on that one. See the other comment.kaddar - Monday, March 17, 2008 - link

No, because in general game development isn't done on instruction sets or assembly, it's done in programming languages utilizing API's. Specifically, DirectX or OpenGL. The architecture is abstracted away, and rightly so.Nihility - Monday, March 17, 2008 - link

Sounds pretty exciting. The huge cache on the Penryn procs does a pretty good job of negating the side effects of the slower memory interconnect so I'd be surprised if we see huge gains from Nehalem just because of the memory part as it wasn't that big of a bottleneck. Probably see more benefits on the server side. However, 8 cores is definitely a treat.