Why Pine Trail Isn't Much Faster Than the First Atom

by Anand Lal Shimpi on January 27, 2010 12:48 PM EST- Posted in

- CPUs

In 2008 Intel introduced the Diamondville platform. This was the Atom platform that was used in the vast majority of netbooks and nettops. You had an Atom processor (codename: Diamondville) and Intel's 945GSE chipset. The memory controller was located on the chipset which was built on a 90nm process that ended up eating quite a bit of power.

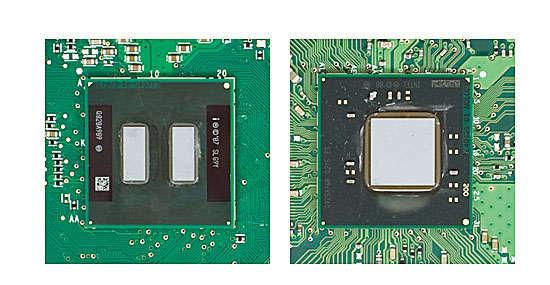

Dual-core Atom "Diamondville" (left) vs. Dual-core Atom "Pineview" (right)

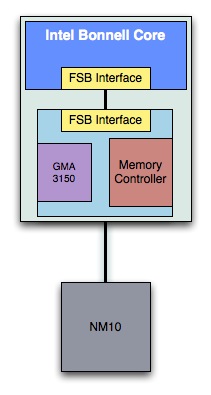

At the end of last year, Intel brought forth Pine Trail. Pine Trail used a new version of the Atom processor (codename: Pineview) and Intel's NM10 Express chipset. The memory controller was moved off the external chipset and on-die with the Atom processor. Graphics also made their way on die and the resulting 45nm chip consumed far less power than the old Atom + 945GSE combo.

When AMD integrated a DDR memory controller with the K8, we saw a big drop in memory latency and tremendous boost in performance. When Intel did the same with Nehalem the results were similar. Yet when we reviewed Pine Trail we saw virtually no drop in memory latency and very few situations where performance actually improved. In fact, it was only on the dual-core desktop Pine Trail system we reviewed that we saw any tangible performance gains.

Remember that Intel's Atom processor uses a dual-issue in-order architecture. As such you'd expect a huge boost from Intel integrating its DDR2 memory controller. After a bit of digging, we've finally figured out why that wasn't the case.

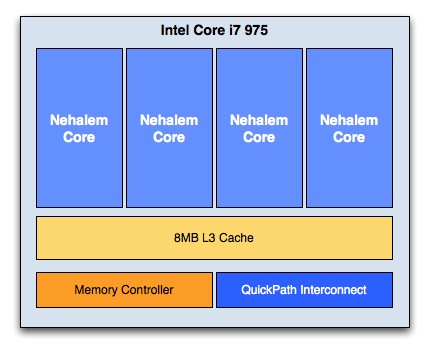

Unlike Nehalem, when Intel integrated the memory controller in Pineview it didn’t start with a brand new design. Here’s what Nehalem looks like from a high level:

The memory controller is on die and connects directly to the cache subsystem via some very low latency interconnects.

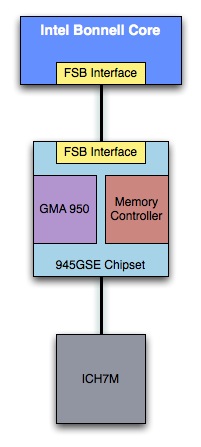

And here’s what Diamondville and Pine Trail look like:

Intel Atom "Diamondville" Platform 2008 | Intel Atom "Pine Trail" Platform 2009-2010 |

|  |

Notice anything funny? There’s still a FSB interface between the CPU core and the memory controller. It’s all on die, but the Pineview CPU core still needs to go through the FSB unit before it can touch the IMC. That’s why the latency didn’t improve much, if at all. There are some improvements that do allow for better performance, but not what you'd expect from a redesigned, integrated memory controller.

Why would Intel do this? It saves time and thus money. Pineview literally uses the same Bonnell core as Diamondville but placed next to an on-die memory controller. A tightly integrated memory controller would require a redesigned version of the Bonnell core, something Intel wasn’t willing to commit to at this point.

Given the lack of competition from AMD or anyone else in the Atom space, it makes sense from a financial standpoint. Eventually Intel will have to redesign the core and tightly couple the memory controller, but I suspect that it won’t happen for a while. At least not until there’s real competition from AMD or someone from the ARM camp.

33 Comments

View All Comments

jamesadames12 - Wednesday, February 3, 2010 - link

http://www.asdpoolsupply.com/pages.php?pageid=11">http://www.asdpoolsupply.com/pages.php?pageid=11wwwcd - Wednesday, January 27, 2010 - link

Double misery of both!joaopft - Tuesday, September 14, 2010 - link

Intel designed the Atom because they were being shamed by designs of other companies on the low power / low cost market. On the other hand, Intel does not want to destroy their PC market. So, marketing constraints create difficulties for Intel.From what I see, this is a fake integrated memory controller. The on-chip FSB had to developed (it is the first time this has been done), and it surely costed money. And it is a cumbersome design anyway, that is now the main cause of the performance problems of this platform. I suspect this has been done with a sole purpose --- market segmentation.

Intel stoped short of integrating the memory controler properly because the Atom platform would then compete with higher priced double core processors in many applications -- core i3's, for instance. This would ruin Intel's business on the consumer desktop market. But the future of the consumer market is the low power and low cost desktop or netbook. And, with the memory frequencies approaching the frequencies of processor cores, with a decent memory controller it would be possible to extract some serious performance out of in-order execution cores.