Hot Chips 31 Analysis: In-Memory Processing by UPMEM

by Dr. Ian Cutress on August 19, 2019 3:15 PM ESTInside the PIM-DRAM and DPU

So as mentioned, each data processing unit (DPU) is put in control of 64 MB of DRAM, leading to 128 DPUs in an 8 GB module. These are built into the DRAM at the same time as manufacturing, but the logic is not as physically dense as regular ASIC logic, making it a high-yielding solution. Ultimately a DRAM die is still mostly DRAM, and the UPMEM states that the DPU size is negligible by comparison. In order to do this, UPMEM created an ASIC-like framework of logic cells, SRAM IPs, and implementation flow. Ultimately the goal was to add these DPUs to an otherwise unmodified DRAM design, and the company states they have succeeded.

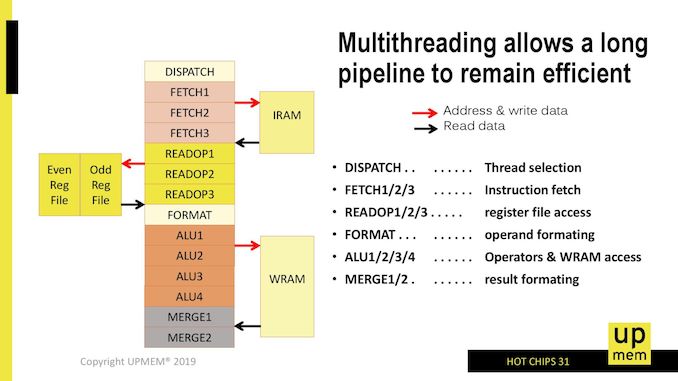

The DPU is a 14-stage interleaved pipeline processor, that uses 24 hardware threads to achieve better scaling (apparently only 11 are needed for 100% utilization). On multithreaded code, this creates a 1 instruction/cycle throughput, and the 1 GB/s latency per DPU to its local memory helps hide the threading. There is no operand bypass, and no stall signals.

Each DPU has 88 KB of SRAMs inside, split into 64 KB of WRAM (a data cache equivalent) and 24 KB of IRAM (instruction cache equivalent), with DMA instructions to move data between the DRAM and the WRAM/IRAM. These DMA engine is autonomous, which UPMEM states has little-no-effect on pipeline for performance. There is no actual ‘cache’ here, with the company stating that there are too many threads for actual caches, so instead they rely on the efficient DRAM engine and a tightly coupled bank of SRAM to do that job.

The 14-stage pipeline us a basic in-order threaded CPU with dispatch/fetch/read/format/ALU/merge stages with access to the local SRAMs. The DPU has a 64-bit wide access port to its 64 MB array of main DRAM for loads and stores through an immediate addressing mode, and ultimately control of the DPU is still through the main CPU. No DPU can talk to each other, and the DPUs can only work on their 64 MB of main memory, allowing security separation between the hardware.

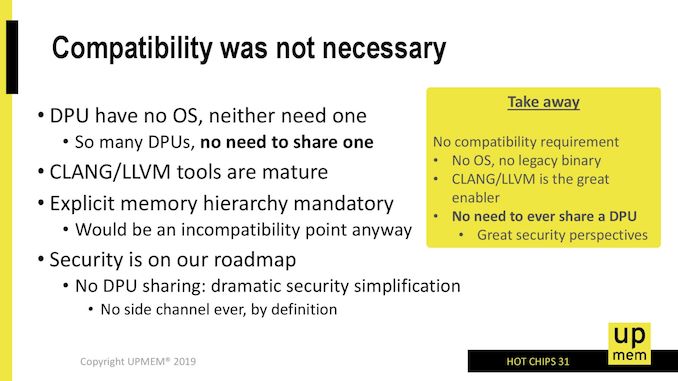

The main server CPU has full control over the DPU units through the APIs provided by UPMEM, such that the DPUs can be done on an allocate/free bases or managed through group execution or one-by-one. The DPU doesn’t actually run an OS according to UPMEM, and is controlled just through the device driver.

UPMEM states that Clang and LLVM tools are mature to manage DPU use through the compiler and provided APIs. Technically the DPUs have orchestration overhead as a result, and part of this is down to using DDR4 rather than a proprietary interface. UPMEM states that this orchestration management, such as bus width mismatches, address interleaving, the lack of cache coherent and the lack of hardware arbitration, is negligible compared to the work the DPU actually does. The APIs for managing this are available for x86, POWER 9, and ARM64.

Internally the DPU uses an optimized 32-bit ISA with triadic instructions, with non-destructive operand compute. As mentioned, the optimized ISA contains a range of typical instructions that can easily be farmed out to in-memory compute, such as SHIFT+ADD/SHIFT+SUB, basic logic (NAND, NOR, ORN, ANDN, NXOR), shift and rotate instructions, and even compute that requires intermediate values. The DPU supports bi-endianess, and is host OS agnostic.

The Goal

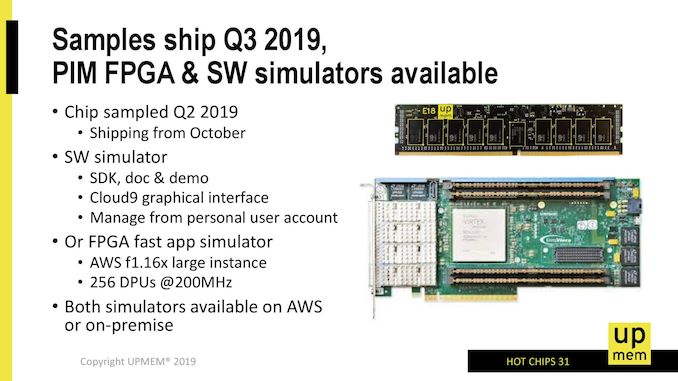

UPMEM is presenting its technology at Hot Chips as an attempt to attract potential customers, and is looking at mass production of its 8 GB memory modules in Q1, although early customers are already being sampled. The company is set to launch a sales office in the Bay Area during the second half of 2019.

The company is putting up impressive numbers for specific workloads, and to be honest, the question of in-memory compute is not really a question of if, but when. Even on the consumer side, there are some good examples where in-memory compute could help. I enjoyed going through UPMEM’s slide decks and looking at what they have to offer. It will be interesting to see other competing solutions come to the market, and how they approach the problem.

I will finish this article on one important note, however. Going up to 20W per 8 GB memory module is not a long-term solution. One of the disadvantages of moving compute away from the CPU is that you have to spend that compute power elsewhere, and a DRAM module isn’t usually the most ideal solution for that based on historic design (especially if doing the calculation is half as efficient). If a CPU socket can hold 150W, and a memory socket can do 20W, then you want most of the power consumed on the compute in the socket. In-memory compute is a good problem to solve, but ultimately it needs to be combined with on-CPU DRAM.

38 Comments

View All Comments

evilpaul666 - Monday, August 19, 2019 - link

Isn't there a move towards having DRAM contents encrypted? If you bit-shift ciphertext don't you just get garbage?Ian Cutress - Monday, August 19, 2019 - link

Very good pointRοb - Tuesday, August 20, 2019 - link

Not with homomorphic encryption: https://en.wikipedia.org/wiki/Homomorphic_encrypti...DanNeely - Wednesday, August 21, 2019 - link

Isn't that still basically limited to research/very targeted small scale use because it has a massive power/performance penalty compared to working on non-encrypted data?Memo.Ray - Monday, August 19, 2019 - link

I was thinking about this in the opposite direction, the security implication of this new feature. Now you can change the data directly in memory - another attack vector that you to protect against.Alexvrb - Monday, August 19, 2019 - link

Awesome now we can have side octa channel attacks!imaskar - Tuesday, August 20, 2019 - link

Depends on the use case. If you're selling vms, then yes. If it's your supercomputing cluster, then no, why would you encrypt it?Elstar - Wednesday, August 21, 2019 - link

The problem is not insurmountable. As long as the DPU has the key AND the key is not extractable, then encrypted memory should work with PIM DRAM.TomWomack - Thursday, August 29, 2019 - link

Not in the high-performance computing space, which is the only place where PIM processing seems plausible; the threat models have really diverged between 'protect this phone which will be running Javascript from arbitrary websites from Ruritanian customs agents with physical access to it' and 'protect this compute cluster which runs only executables compiled on the head-node by trusted users'Dodozoid - Monday, August 19, 2019 - link

IMP for In-Memory Processing sound way better than PIM fo Processing In Memory. Hope we could some day get to PARALLEL in-memory processing for even merrier abbreviation.