Semiconductors

One of the core challenges that Rapidus will face when it kicks off volume production of chips on its 2nm-class process technology in 2027 is lining up customers. With Intel, Samsung, and TSMC all slated to offer their own 2nm-class nodes by that time, Rapidus will need some kind of advantage to attract customers away from its more established rivals. To that end, the company thinks they've found their edge: fully automated packaging that will allow for shorter chip lead times than manned packaging operations. In an interview with Nikkei, Rapidus' president, Atsuyoshi Koike, outlined the company's vision to use advanced packaging as a competitive edge for the new fab. The Hokkaido facility, which is currently under construction and is expecting to begin equipment installation...

U.S. Signs $1.5B in CHIPS Act Agreements With Amkor and SKhynix for Chip Packaging Plants

Under the CHIPS & Science Act, the U.S. government provided tens of billions of dollars in grants and loans to the world's leading maker of chips, such as Intel...

0 by Anton Shilov on 8/9/2024Imec Successfully Demonstrates High-NA Lithography for Logic and DRAM Patterning for First Time

Imec and ASML have announced that the two companies have printed the first logic and DRAM patterns using ASML's experimental Twinscan EXE:5000 EUV lithography tool, the industry's first High-NA...

5 by Anton Shilov on 8/8/2024TSMCs Q2'24 Results: Best Quarter Ever as HPC Revenue Share Exceeds 52% on AI Demand

Taiwan Semiconductor Manufacturing Co. this week said its revenue for the second quarter 2024 reached $20.82 billion, making it the company's best quarter (at least in dollars) to date...

1 by Anton Shilov on 7/18/2024Applied Materials' New Deposition Tool Enables Copper Wires to Be Used for 2nm and Beyond

Although the pace of Moore's Law has undeniably slackened in the last decade, transistor density is still increasing with every new process technology. But there is a challenge with...

7 by Anton Shilov on 7/12/2024Micron: U.S. Fabs Will Start Operating in 2026 - 2029

When Micron announced plans to build two new fabs in the U.S. in 2022, the company vaguely said both would come online by the decade's end. Then, in 2023...

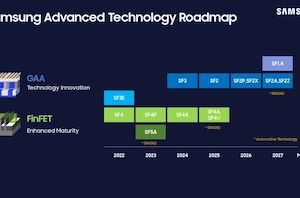

2 by Anton Shilov on 6/27/2024Samsung Foundry Unveils Updated Roadmap: BSPDN and 2nm Evolution Through 2027

Samsung this week has unveiled its latest process technologies roadmap at the company's Samsung Foundry Forum (SFF) U.S. The new plan covers the evolution of Samsung's 2nm-class production nodes...

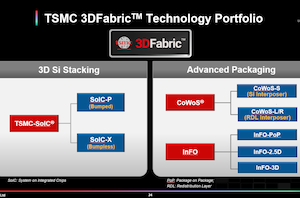

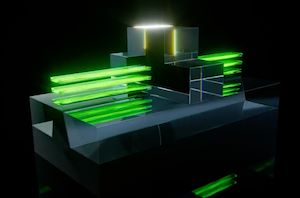

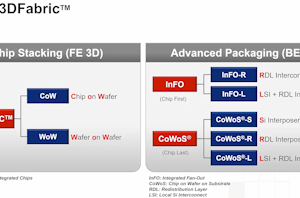

10 by Anton Shilov on 6/13/2024TSMC's 3D Stacked SoIC Packaging Making Quick Progress, Eyeing Ultra-Dense 3μm Pitch In 2027

TSMC's 3D-stacked system-on-integrated chips (SoIC) advanced packaging technologies is set to evolve rapidly. In a presentation at the company's recent technology symposium, TSMC outlined a roadmap that will take...

1 by Anton Shilov on 5/31/2024TSMC: Performance and Yields of 2nm on Track, Mass Production To Start In 2025

In addition to revealing its roadmap and plans concerning its current leading-edge process technologies, TSMC also shared progress of its N2 node as part of its Symposiums 2024. The...

9 by Anton Shilov on 5/30/2024Rapidus Adds Chip Packaging Services to Plans for $32 Billion 2nm Fab

To say that the global foundry market is booming right now would be an understatement. Demand for leading-edge process technologies driven by AI and HPC applications is unprecedented, and...

12 by Anton Shilov on 5/24/2024TSMC's Roadmap at a Glance: N3X, N2P, A16 Coming in 2025/2026

As announced last week by TSMC, later this year the company is set to start high-volume manufacturing on its N3P fabrication process, and this will be the company's most...

47 by Anton Shilov on 5/22/2024TSMC Offers a Peek at 'Global Gigafab' Process Replication Program

At its European Technology Symposium last week TSMC revealed some of the details about its Global Gigafab Manufacturing program, the company's strategy to replicate its manufacturing processes across its...

11 by Anton Shilov on 5/22/2024TSMC to Expand CoWoS Capacity by 60% Yearly Through 2026

Customer demand for AI and HPC processors is driving a much greater use of advanced packaging technologies, particularly TSMC's chip-on-wafer-on-substrate (CoWoS) services. As things stand, TSMC is just barely...

8 by Anton Shilov on 5/21/2024TSMC Outlines Path to EUV Success: More Tools, More Wafers, & Best Pellicles In Industry

Although TSMC can't claim to be the first fab to use extreme UV (EUV) lithography – that title goes to Samsung – they do get to claim to be...

20 by Anton Shilov on 5/17/2024TSMC to Expand Specialty Capacity by 50%, Introduce 4nm N4e Low-Power Node

With all the new fabs being built in Germany and Japan, as well as the expansion of production capacity in China, TSMC is planning to extend its production capacity...

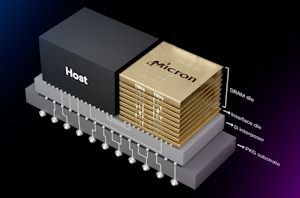

0 by Anton Shilov on 5/16/2024TSMC Readies Next-Gen HBM4 Base Dies, Built on 12nm and 5nm Nodes

Of the several major changes coming with HBM4 memory, one of the most immediate is the sheer width of the memory interface. With the fourth-generation memory standard moving from...

1 by Anton Shilov on 5/16/2024TSMC: Performance-Optimized 3nm N3P Process on Track for Mass Production This Year

As part of the second leg of TSMC's spring technology symposium series, the company offered an update on the state of its 3nm-class processes, both current and future. Building...

21 by Anton Shilov on 5/15/2024Samsung Tapes Out Its First 3nm Smartphone SoC, Gets A Boost From Synopsys AI-Enabled Tools

This week Samsung Electronics and Synopsys announced that Samsung has taped out its first mobile system-on-chip on Samsung Foundry's 3nm gate-all-around (GAA) process technology. The announcement, coming from electronic...

8 by Anton Shilov on 5/3/2024Samsung Foundry Update: 2nm Unveil in June, Second-Gen SF3 3nm Hits Production This Year

As part of Samsung's Q1 earnings announcement, the company has outlined some of its foundry unit's key plans for the rest of the year. The company has confirmed that...

4 by Anton Shilov on 5/1/2024TSMC Readies 8x Reticle Super Carrier Interposer For Next-Gen Chips Twice as Large As Today's

TSMC is no stranger to building big chips. Besides the ~800mm2 reticle limit of their normal logic processes, the company already produces even larger chips by fitting multiple dies...

6 by Anton Shilov on 4/30/2024